Des chercheurs de l’Indian Institute of Science (IISc) ont mis au point un cadre de conception pour construire la prochaine génération de puces informatiques analogiques qui pourraient être plus rapides et nécessiter moins d’énergie que les puces numériques que l’on trouve dans la plupart des appareils électroniques.

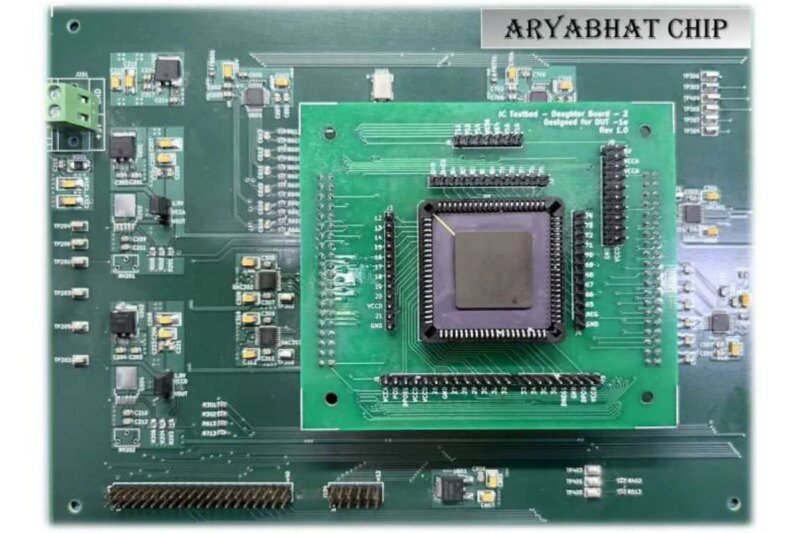

En utilisant leur nouveau cadre de conception, l’équipe a construit un prototype de chipset analogique appelé ARYABHAT-1 (Analog Reconfigurable Technology And Bias-scalable Hardware for AI Tasks), a déclaré l’IISc basé à Bengaluru dans un communiqué mardi.

“Ce type de chipset peut être particulièrement utile pour les applications basées sur l’intelligence artificielle (IA) comme la reconnaissance d’objets ou de la parole – pensez à Alexa ou Siri – ou celles qui nécessitent des opérations de calcul parallèles massives à des vitesses élevées”, a-t-il ajouté.

La plupart des appareils électroniques, en particulier ceux qui font appel à l’informatique, utilisent des puces numériques parce que le processus de conception est simple et évolutif, a-t-il noté.

“Mais l’avantage de l’analogique est énorme. Vous obtiendrez des ordres de grandeur d’amélioration de la puissance et de la taille”, explique Chetan Singh Thakur, professeur adjoint au Département d’ingénierie des systèmes électroniques (DESE) de l’IISc, dont le laboratoire dirige les efforts de développement de la puce analogique.

Dans les applications qui ne nécessitent pas de calculs précis, l’informatique analogique a le potentiel de surpasser l’informatique numérique, car la première est plus économe en énergie.

Cependant, il existe plusieurs obstacles technologiques à surmonter lors de la conception de puces analogiques. Contrairement aux puces numériques, les tests et la co-conception des processeurs analogiques sont difficiles. Les processeurs numériques à grande échelle peuvent être facilement synthétisés en compilant un code de haut niveau, et la même conception peut être portée à travers différentes générations de développement technologique – par exemple, d’une puce de 7 nm à une puce de 3 nm – avec des modifications minimales, selon la déclaration.

Comme les puces analogiques ne s’adaptent pas facilement, elles doivent être personnalisées individuellement lors de la transition vers la technologie de la génération suivante ou vers une nouvelle application – leur conception est coûteuse, selon le communiqué.

Un autre défi est que le compromis entre la précision et la vitesse, d’une part, et la puissance et la surface, d’autre part, n’est pas facile en matière de conception analogique, ajoute-t-il.

Dans le domaine de la conception numérique, le simple fait d’ajouter davantage de composants tels que des unités logiques sur la même puce peut augmenter la précision, et la puissance à laquelle ils fonctionnent peut être ajustée sans affecter les performances du dispositif, note le communiqué.

Pour surmonter ces difficultés, l’équipe a conçu un nouveau cadre qui permet le développement de processeurs analogiques qui s’échelonnent comme les processeurs numériques. Son jeu de puces peut être reconfiguré et programmé de manière à ce que les mêmes modules analogiques puissent être portés sur différentes générations de conception de processus et sur différentes applications, indique le communiqué.

“Vous pouvez synthétiser le même type de puce à 180 nm ou à 7 nm, tout comme la conception numérique”, a déclaré Thakur.

Différentes architectures d’apprentissage automatique peuvent être programmées sur ARYABHAT, et comme les processeurs numériques, elles peuvent fonctionner de manière robuste sur une large gamme de températures, ont déclaré les chercheurs. Ils ajoutent que l’architecture est également “bias-scalable” – ses performances restent les mêmes lorsque les conditions de fonctionnement comme la tension ou le courant sont modifiées. Cela signifie que le même chipset peut être configuré soit pour des applications ultra-énergétiques de l’Internet des objets (IoT), soit pour des tâches à grande vitesse comme la détection d’objets.

Le cadre de conception a été développé dans le cadre du travail de doctorat de Pratik Kumar, étudiant de l’IISc, et en collaboration avec Shantanu Chakrabartty, professeur à la McKelvey School of Engineering de l’Université de Washington à St Louis (WashU), aux États-Unis, qui est également l’ambassadeur de la McDonnell Academy de WashU auprès de l’IISc.

“C’est une bonne chose de voir la théorie de l’informatique analogique évolutive en biais se manifester dans la réalité et dans des applications pratiques”, a déclaré Chakrabartty, qui avait déjà proposé des circuits analogiques évolutifs en biais.

Les chercheurs ont exposé leurs résultats dans deux études pré-imprimées qui sont actuellement en cours d’examen par les pairs. Ils ont également déposé des brevets et prévoient de travailler avec des partenaires industriels pour commercialiser la technologie, selon le communiqué.