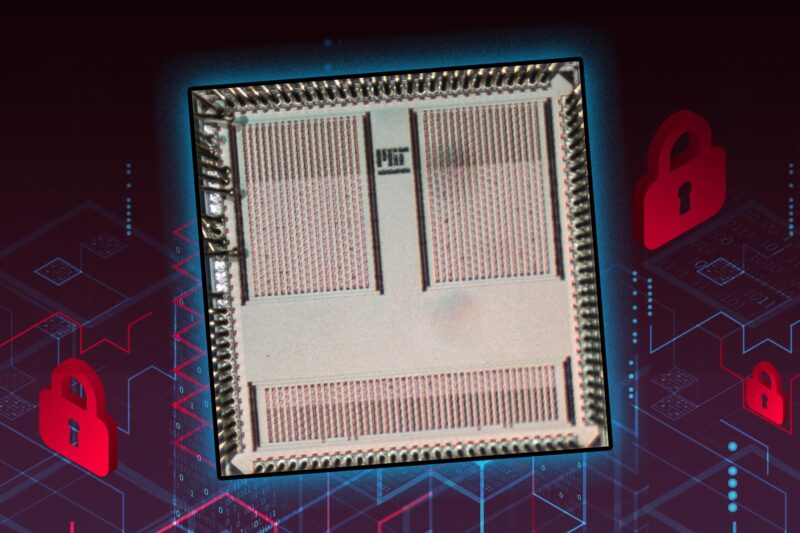

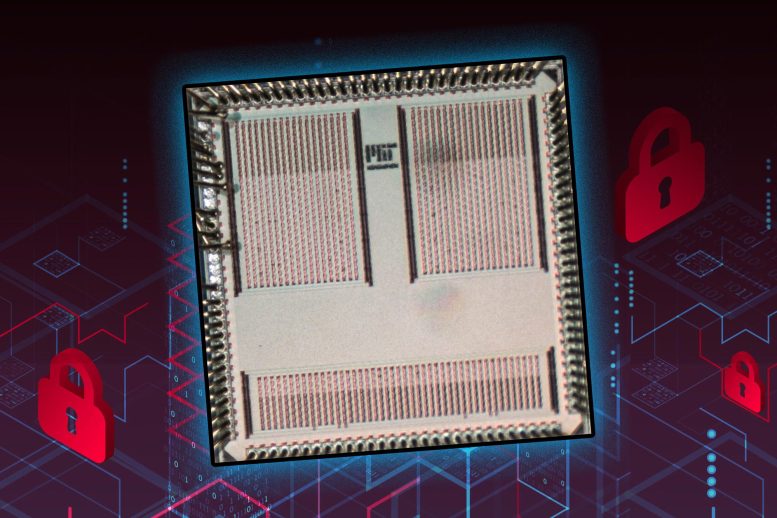

Les chercheurs du MIT ont mis au point un circuit intégré spécifique à une application (ASIC), illustré ici, qui peut être mis en œuvre sur un dispositif de l’internet des objets pour se défendre contre les attaques par canal latéral basées sur la puissance. Crédit : Photo de la puce reproduite avec l’aimable autorisation des chercheurs et éditée par MIT News.

Vers une défense plus forte des données personnelles

Des ingénieurs construisent une puce à faible consommation d’énergie qui peut empêcher les pirates d’extraire des informations cachées d’un appareil intelligent.

Un patient victime d’une crise cardiaque, récemment sorti de l’hôpital, utilise une smartwatch pour l’aider à surveiller les signaux de son électrocardiogramme. La smartwatch peut sembler sûre, mais le réseau neuronal qui traite ces informations de santé utilise des données privées qui peuvent toujours être volées par un agent malveillant par l’intermédiaire d’un système d’information. attaque par canal latéral.

Une attaque par canal latéral vise à recueillir des informations secrètes en exploitant indirectement un système ou son matériel. Dans un type d’attaque à canal latéral, un pirate avisé pourrait surveiller les fluctuations de la consommation d’énergie de l’appareil pendant que le réseau neuronal fonctionne pour extraire des informations protégées qui “fuient” de l’appareil.

“Dans les films, lorsque les gens veulent ouvrir des coffres verrouillés, ils écoutent les clics de la serrure lorsqu’ils la tournent. Cela révèle que le fait de tourner la serrure dans cette direction les aidera probablement à aller plus loin. C’est ce qu’est une attaque par canal latéral. Il s’agit simplement d’exploiter des informations non intentionnelles et de les utiliser pour prédire ce qui se passe à l’intérieur du dispositif”, explique Saurav Maji, étudiant diplômé en MIT’s Department of Electrical Engineering and Computer Science (EECS) and lead author of a paper that tackles this issue.

Current methods that can prevent some side-channel attacks are notoriously power-intensive, so they often aren’t feasible for internet-of-things (IoT) devices like smartwatches, which rely on lower-power computation.

Now, Maji and his collaborators have built an integrated circuit chip that can defend against power side-channel attacks while using much less energy than a common security technique. The chip, smaller than a thumbnail, could be incorporated into a smartwatch, smartphone, or tablet to perform secure machine learning computations on sensor values.

“The goal of this project is to build an integrated circuit that does machine learning on the edge, so that it is still low-power but can protect against these side channel attacks so we don’t lose the privacy of these models,” says Anantha Chandrakasan, the dean of the MIT School of Engineering, Vannevar Bush Professor of Electrical Engineering and Computer Science, and senior author of the paper. “People have not paid much attention to security of these machine-learning algorithms, and this proposed hardware is effectively addressing this space.”

Co-authors include Utsav Banerjee, a former EECS graduate student who is now an assistant professor in the Department of Electronic Systems Engineering at the Indian Institute of Science, and Samuel Fuller, an MIT visiting scientist and distinguished research scientist at Analog Devices. The research is being presented at the International Solid-States Circuit Conference.

Computing at random

The chip the team developed is based on a special type of computation known as threshold computing. Rather than having a neural network operate on actual data, the data are first split into unique, random components. The network operates on those random components individually, in a random order, before accumulating the final result.

Using this method, the information leakage from the device is random every time, so it does not reveal any actual side-channel information, Maji says. But this approach is more computationally expensive since the neural network now must run more operations, and it also requires more memory to store the jumbled information.

So, the researchers optimized the process by using a function that reduces the amount of multiplication the neural network needs to process data, which slashes the required computing power. They also protect the neutral network itself by encrypting the model’s parameters. By grouping the parameters in chunks before encrypting them, they provide more security while reducing the amount of memory needed on the chip.

“By using this special function, we can perform this operation while skipping some steps with lesser impacts, which allows us to reduce the overhead. We can reduce the cost, but it comes with other costs in terms of neural network accuracy. So, we have to make a judicious choice of the algorithm and architectures that we choose,” Maji says.

Existing secure computation methods like homomorphic encryption offer strong security guarantees, but they incur huge overheads in area and power, which limits their use in many applications. The researchers’ proposed method, which aims to provide the same type of security, was able to achieve three orders of magnitude lower energy use. By streamlining the chip architecture, the researchers were also able to use less space on a silicon chip than similar security hardware, an important factor when implementing a chip on personal-sized devices.

“Security matters”

While providing significant security against power side-channel attacks, the researchers’ chip requires 5.5 times more power and 1.6 times more silicon area than a baseline insecure implementation.

“We’re at the point where security matters. We have to be willing to trade off some amount of energy consumption to make a more secure computation. This is not a free lunch. Future research could focus on how to reduce the amount of overhead in order to make this computation more secure,” Chandrakasan says.

They compared their chip to a default implementation which had no security hardware. In the default implementation, they were able to recover hidden information after collecting about 1,000 power waveforms (representations of power usage over time) from the device. With the new hardware, even after collecting 2 million waveforms, they still could not recover the data.

They also tested their chip with biomedical signal data to ensure it would work in a real-world implementation. The chip is flexible and can be programmed to any signal a user wants to analyze, Maji explains.

“Security adds a new dimension to the design of IoT nodes, on top of designing for performance, power, and energy consumption. This ASIC [application-specific integrated circuit] démontre joliment que la conception de la sécurité, dans ce cas par l’ajout d’un schéma de masquage, ne doit pas être considérée comme un ajout coûteux”, déclare Ingrid Verbauwhede, professeur dans le groupe de recherche sur la sécurité informatique et la cryptographie industrielle du département d’ingénierie électrique de l’Université catholique de Louvain, qui n’a pas participé à cette recherche. “Les auteurs montrent qu’en sélectionnant des unités de calcul favorables au masquage, en intégrant la sécurité lors de la conception, et même en incluant le générateur d’aléatoire, un accélérateur de réseau neuronal sécurisé est réalisable dans le contexte d’un IoT”, ajoute-t-elle.

À l’avenir, les chercheurs espèrent appliquer leur approche aux attaques par canal latéral électromagnétique. Ces attaques sont plus difficiles à défendre, car un pirate n’a pas besoin du dispositif physique pour collecter des informations cachées.

Ce travail a été financé par Analog Devices, Inc. L’aide à la fabrication des puces a été fournie par le programme University Shuttle de la Taiwan Semiconductor Manufacturing Company.